# Futurebus+ Interface Family Data Manual

Protocol, Arbitration and Backplane Transceiver Logic

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated (TI) reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of reievant information to verify, before placing orders, that the information being relied on is current.

TI warrants performance of its semiconductor products and related software to current specifications in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Please be aware that TI products are not intended for use in life-support appliances, devices, or systems. Use of TI product in such applications requires the written approval of the appropriate TI officer. Certain applications using semiconductor devices may involve potential risks of personal injury, property damage, or loss of life. In order to minimize these risks, adequate design and operating safeguards should be provided by the customer to minimize inherent or procedural hazards. Inclusion of TI products in such applications is understood to be fully at the risk of the customer using TI devices or systems.

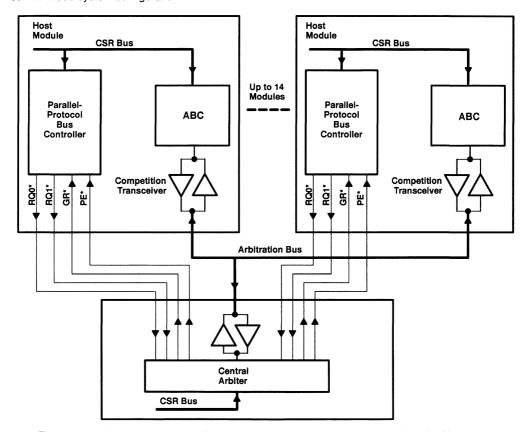

TI assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or services described herein. Nor does TI warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used.

Copyright © 1994, Texas Instruments Incorporated

Printed in UK

#### PREFACE

This preface presents the benefits of the TI Futurebus+ interface chip set and develops the context for this data manual.

Futurebus+ has rapidly gained wide acceptance throughout the world in multiple-compute paradigms. Historically, the success of backplane buses has been based on multiple sources of standard silicon.

#### Standard Silicon for a Standardized Bus

#### Benefits of Standard Silicon

- System design time reduction

- Program risk reduction

- · Greater degree of integration

- Accommodates specification complexity

- Joint development opportunities

- · Ease of product performance improvement

The Futurebus+ family of specifications is very complex. Therefore, it is not a trivial task to implement these specifications in bus-interface silicon. Texas Instruments, with its long-term involvement in the development of Futurebus+, is ideally suited to meet customer requirements in this area. Through understanding of the specifications, customer feedback, and joint development activities, a highly integrated chip set has been designed. Use of this chip set will shorten system development time significantly. Implementing the interface in a small number of controllers reduces overall risk and provides tremendous real estate savings, allowing more features to be added to each module. Additionally, a standard solution eases the development of new products; product performance may be improved or features added without changing the software interface to the Futurebus+. Second sourcing by Philips Components-Signetics ensures the customer of reliable dual sources for these devices.

#### TFB2000 Family: High-Performance Silicon Support for Futurebus+

#### Features of the TI Futurebus+ Chip Set

- Fully compliant to Futurebus+ and related specifications

- · Incorporates control and status registers on chip

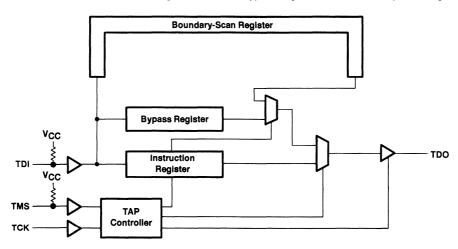

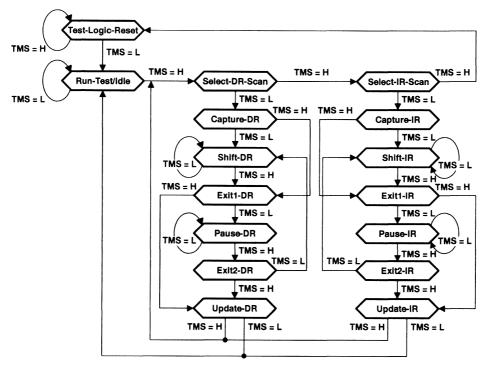

- JTAG support provided

- Silicon support for loosely coupled and tightly coupled systems

- Support for compelled and packet modes

- Interface to both central and distributed arbitration schemes

#### **JTAG Support Required**

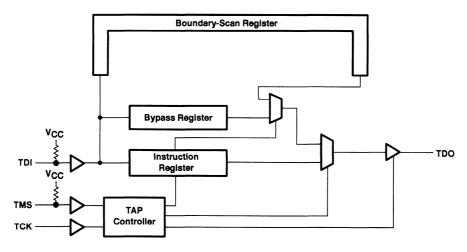

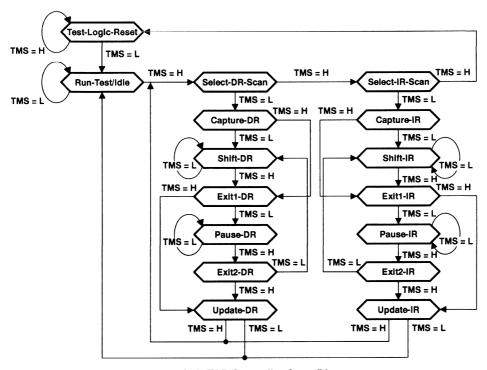

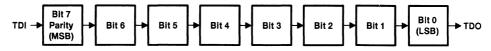

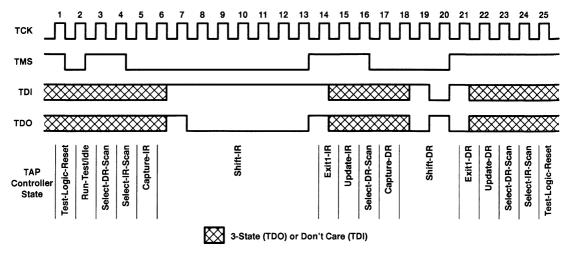

Texas Instruments is an acknowledged leader in the development of testability standards. When employing complex integrated circuits in even more complex systems, assistance in testing is a must. Each of the controller devices in the TI Futurebus+ chip set provides JTAG test access ports and boundary scan capability.

#### **Generic Host Interface to Controller Devices**

#### **Features**

- Designed to support current and future microprocessors from several manufacturers

- Minimal control-signal translation required to interface to processor(s) or secondary cache

- Supports 32- or 36-bit addressing and 32- or 64-bit (multiplexed) data capability

- Provides single, burst, and multiple-burst transfer capability

The host interface, portions of which are provided on each of the Texas Instruments Futurebus+ controller devices, provides a generic host interface, enabling several lines of popular processors to be used with the chip set with minimal glue logic. This interface is used to interconnect processors, local memory, and I/O

devices with the Futurebus+ interface logic. Facilities are provided for burst-mode transfers and synchronous handshaking. A detailed explanation of the host interface is included in this manual.

#### The TI TFB2xxx Futurebus+ Family

TI develops and produces transceivers, arbiters, protocol controllers, and data path devices to meet a wide range of system uses.

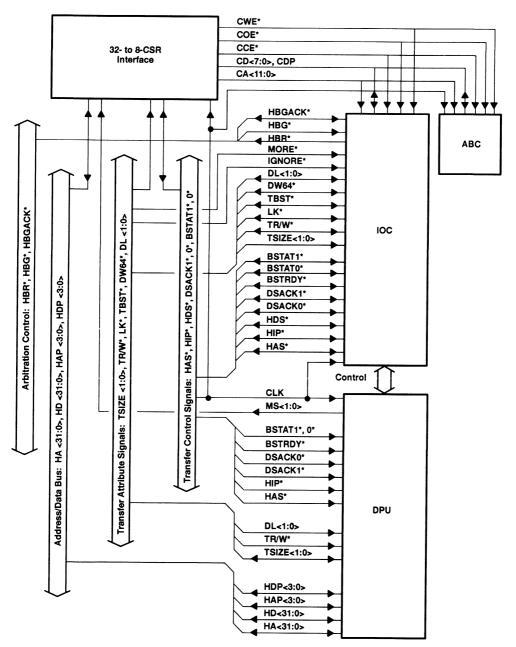

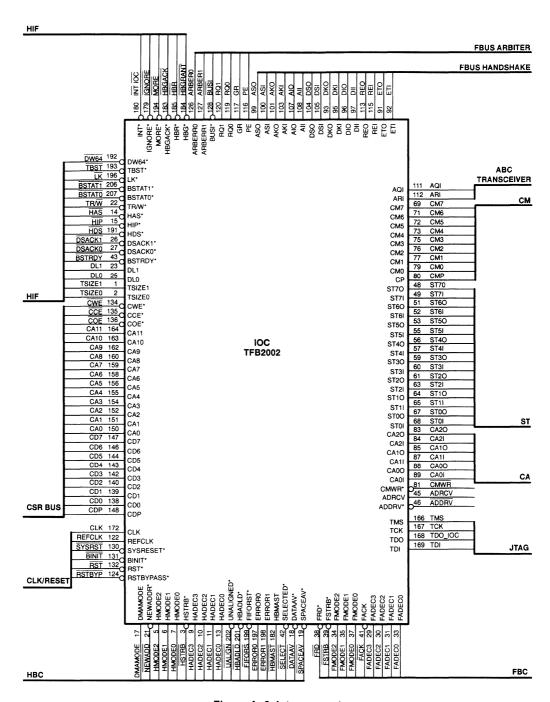

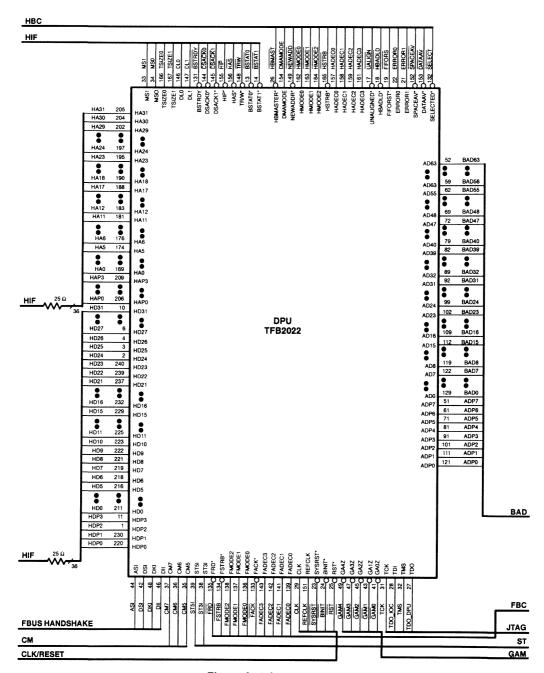

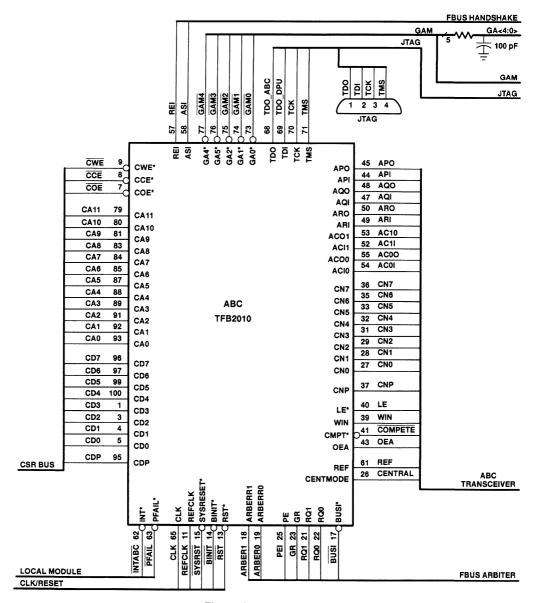

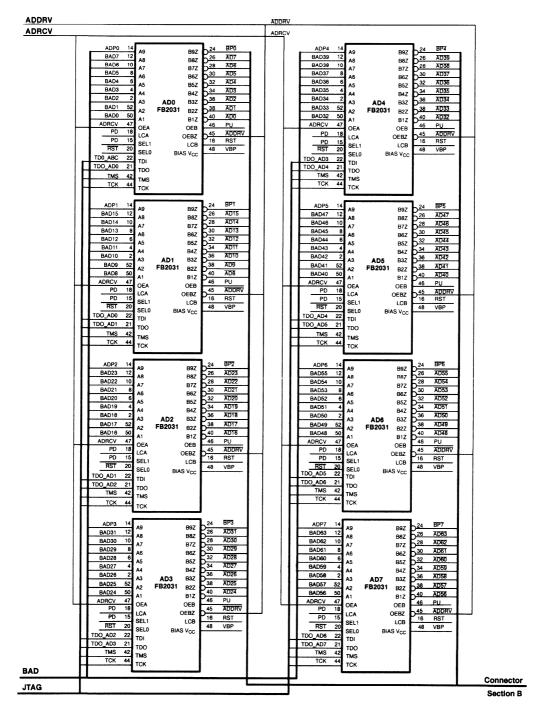

Current TI chip set devices are the TFB2002B I/O controller (IOC), the TFB2022A data-path unit (DPU), and the TFB2010 arbitration bus controller (ABC). The TFB2002B/2022A pair fully supports profile B I/O bus usage and significant portions of other profiles. These devices may be used for memory boards or I/O boards in Profile F (cache-coherent) systems.

#### **Associated Documentation**

This data manual occasionally refers to IEEE 896.x Futurebus+ standard documentation. Although the data manual is a stand-alone document, the reader may want to order the IEEE 896.x documents by calling the IEEE in New York City (1-800-678-IEEE).

#### Texas Instruments Futurebus+ Bulletin Board System (BBS)

A computer bulletin board system (BBS) with modem input is available for customer support purposes. The BBS's characteristics and performance are provided in the following table.

| TEXAS INSTRUMENTS FUTUREBUS+ BULLETIN BOARD SYSTEM     |                                  |  |  |

|--------------------------------------------------------|----------------------------------|--|--|

| CUSTOMER SUPPORT (VIA MODEM) NUMBER: 214-997-3195      |                                  |  |  |

| Data Rate 300-14,400 baud                              |                                  |  |  |

| Recommended Protocol                                   | Zmodem                           |  |  |

| Data, Stop, and Parity                                 | 8, none, and 1 or 7, even, and 1 |  |  |

| Current Capability Messages, file read/download/upload |                                  |  |  |

| Future Capability Questionnaire, Internet              |                                  |  |  |

If a satisfactory connection to the BBS is unavailable, call the product information center (PIC) at 214-644-5580 for assistance.

#### **Signal Name Notation**

To maintain consistency with the notation used in the Futurebus+ standard (IEEE Std 896. 1–1991), an active-low signal is denoted herein by use of the trailing asterisk (\*) on the signal name.

#### **Document Organization**

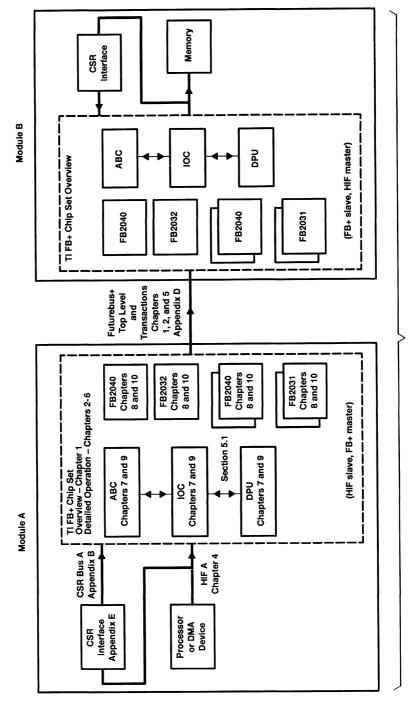

This section is intended to give the reader a feel for the information to be presented in Chapters 1–6 of the data manual and the rationale for the order of presentation. The chip set is described in general first and then in increasing detail. These chapters describe the actual use of the chip set in a chronological order that relates to the order of events that the devices would see in practice, from reset and control-register programming to transactions moving data across the bus.

#### **Chapter 1 Introduction**

This chapter presents some history of the Futurebus+ standard and some of the trade-offs considered when architecting the chip set.

#### **Chapter 2 Orientation**

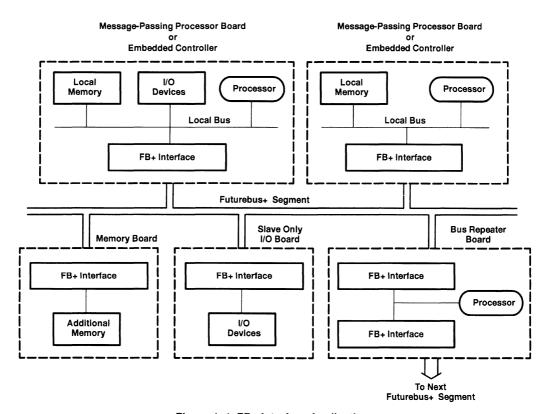

This chapter presents an overview of the environment in which the chip set are used and defines some terms that are used throughout the data manual.

#### **Chapter 3 Configuration**

This chapter identifies the procedures necessary to bring the chip set online in an application.

#### **Chapter 4 Host Interface**

This chapter describes the host interface that provides communications between the chip set and the board controller.

#### **Chapter 5 Transactions**

This chapter describes the transactions across Futurebus+ generated from the host.

#### **Chapter 6 Arbitration**

This chapter describes the Futurebus+ arbitration protocols.

Guide to the TI Futurebus+ Chip Set Data Manual

End-to-End Transaction Description (Defines Relationship of Transactions Between Different Buses) Chapter 5

#### **Contents**

| Sec | tion | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Page       |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1   | Ove  | rview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1–3        |

|     | 1.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1–3        |

|     |      | 1.1.1 What is FB+?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1–3        |

|     |      | 1.1.2 FB+ In Perspective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-4        |

|     |      | 1.1.3 Current and Future Applications, Trends                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1-5        |

|     | 1.2  | Futurebus+ Framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–6        |

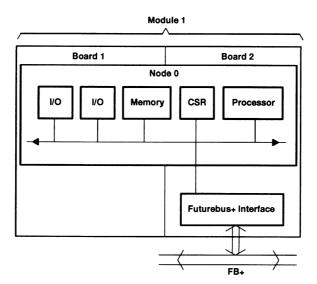

|     |      | 1.2.1 Futurebus+ Philosophy and System-Level Backplane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1–6        |

|     |      | 1.2.2 Individual Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1–6        |

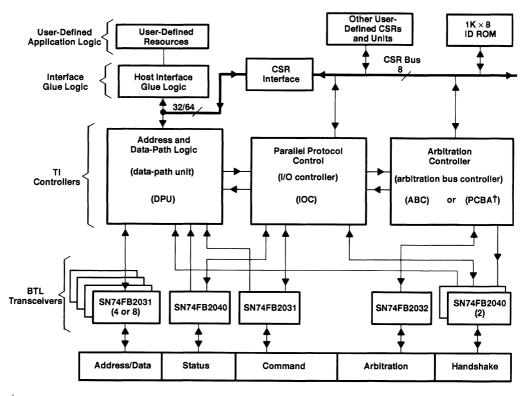

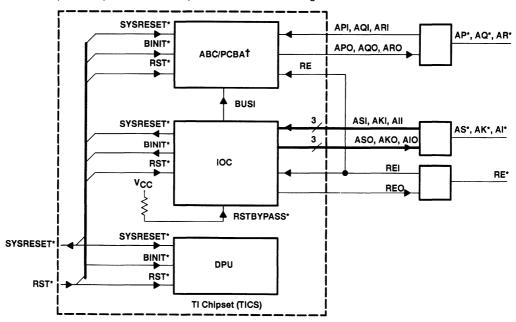

|     | 1.3  | TI Interface Chip Set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1-7        |

|     |      | 1.3.1 Controller ICs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1–7        |

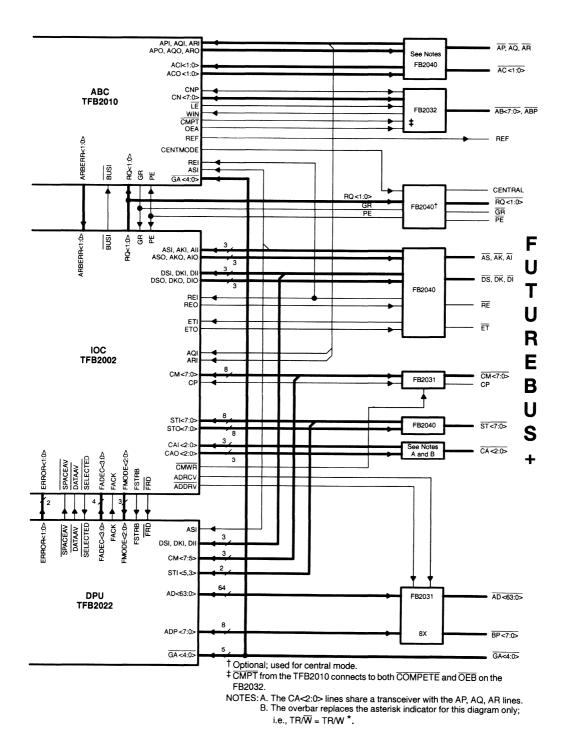

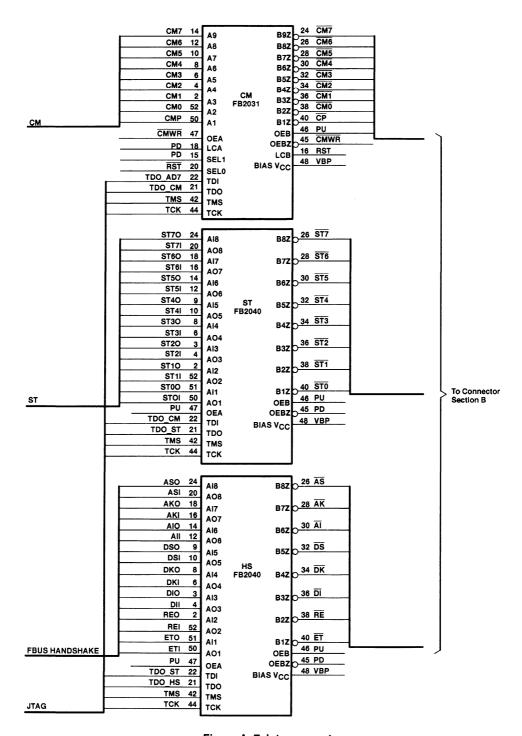

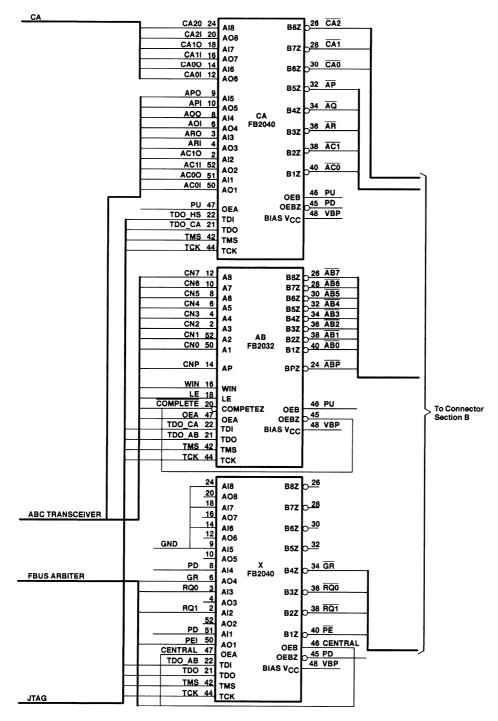

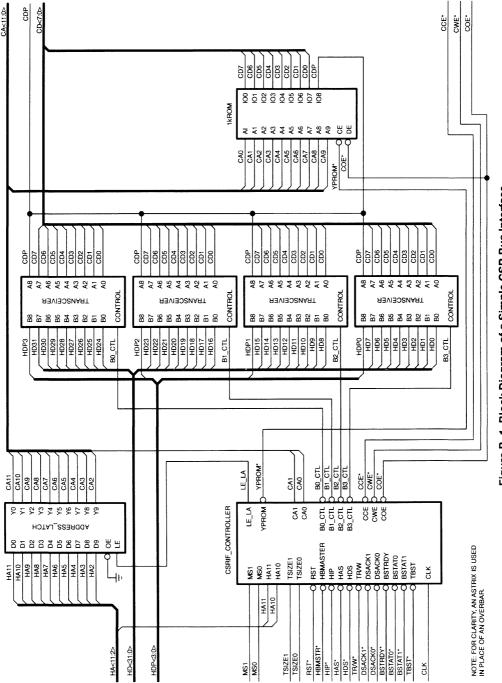

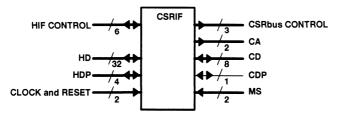

|     |      | 1.3.2 Chip-Set Interconnect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1-11       |

| 2   | Orie | entation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2–3        |

| _   | 2.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2–3        |

|     | 2.2  | Transfer Example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2–3        |

|     | 2.3  | Transfer Overhead                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-4        |

|     | 2.4  | Command and Status Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-4        |

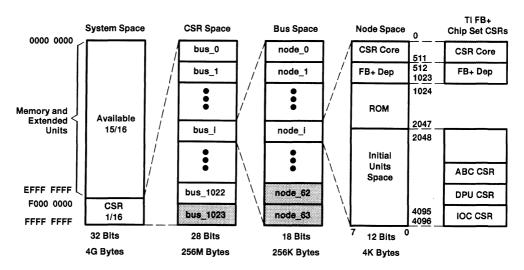

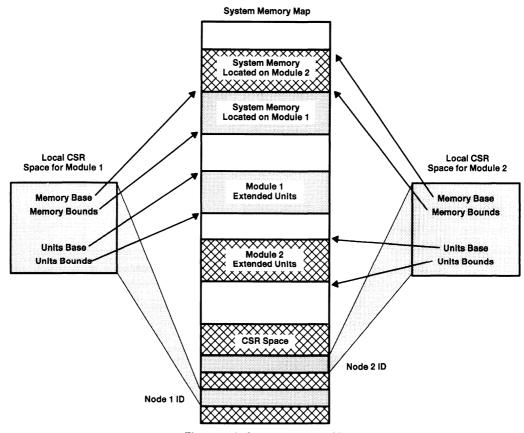

|     | 2.5  | System Memory Partitioning                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2–6        |

|     | 2.6  | Operating Environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-7        |

|     | 2.7  | Transfer Capabilities                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2-7        |

| 3   |      | alization and Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–3        |

| 3   | 3.1  | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3-3<br>3-3 |

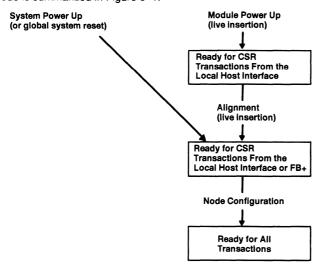

|     | 3.1  | Power Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3–3<br>3–3 |

|     | 3.2  | 3.2.1 System Power-Up Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–3        |

|     |      | 3.2.2 Module Power Up During Live Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–3<br>3–4 |

|     | 3.3  | Initial Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3–4        |

|     | 3.4  | Monarch Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3–4<br>3–6 |

|     | 3.5  | Node Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3–6        |

|     | 3.5  | 3.5.1 Minimum Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3–6<br>3–7 |

|     |      | 3.5.2 Memory Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3–7<br>3–7 |

|     |      | 3.5.3 Transfer Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -          |

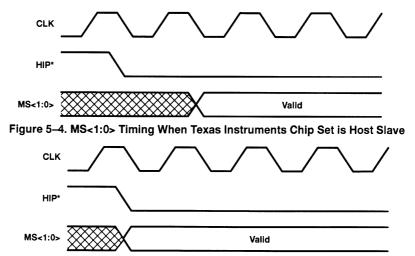

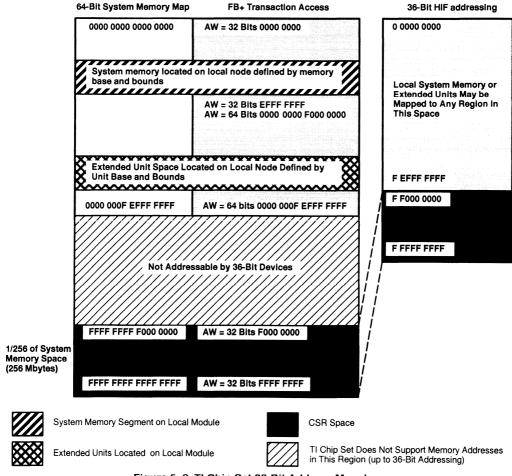

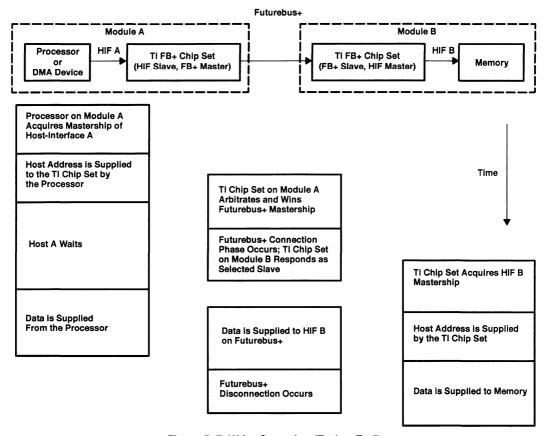

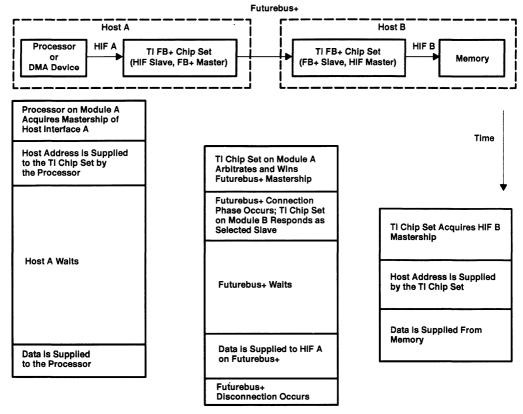

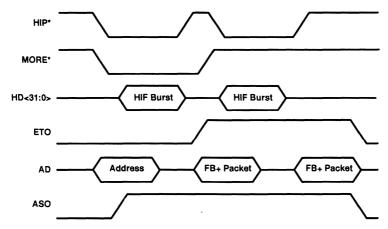

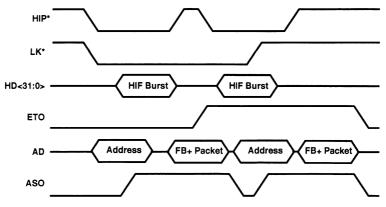

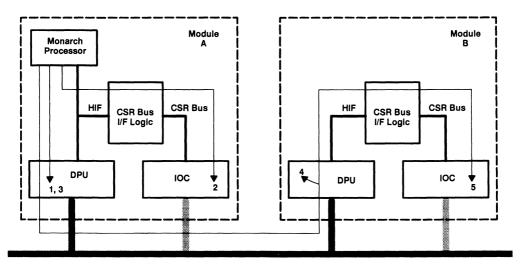

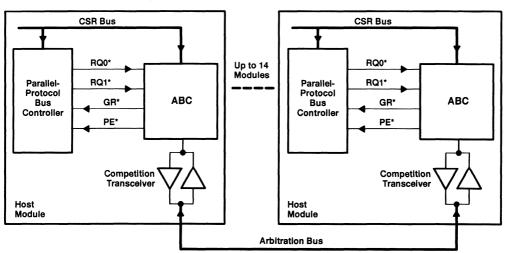

|     |      | 3.5.4 Timers (busy, error, split, transaction)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3-7<br>3-7 |